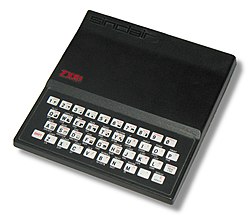

Sinclair ZX81

El computador personal Sinclair ZX81, lanzado por Sinclair Research en 1981, es el computador de menor precio de la época y se vendió por 49,95 libras esterlinas como un kit, y montado por 69,95. Es la versión mejorada del ZX80, comercializado el año anterior. La carcasa fue negra, con un teclado de membrana. La apariencia definitiva de la máquina fue el trabajo del entonces diseñador industrial Rick Dickinson. La salida de vídeo, así como en el ZX80, fue hacia un televisor mediante un modulador de radiofrecuencia, y los programas se leían y guardaban mediante un grabador de casetes común usando cintas magnéticas de audio.

| Sinclair ZX81 | |||||

|---|---|---|---|---|---|

| |||||

| Información | |||||

| Tipo | Computadora doméstica | ||||

| Fecha de creación | 1981 | ||||

| Desarrollador | Sinclair Research | ||||

| Fabricante | Timex | ||||

| Procesador | Zilog Z80 | ||||

| Datos técnicos | |||||

| Procesador | Zilog Z80 | ||||

| Memoria | 1 kB | ||||

| Vídeo | TV o monitor de TV | ||||

| Software | |||||

| Sistema operativo | Sinclair BASIC | ||||

| Cronología | |||||

| |||||

Descripción general

editarLa pantalla fue de texto solamente, 32 caracteres de ancho por 24 de alto; sin embargo, fueron posibles gráficos con una resolución de 64x48 píxeles con el uso del comando PLOT, que seleccionaba entre un grupo de 16 caracteres gráficos para la simulación de los píxeles. Para conservar memoria, el texto mostrado en la pantalla se almacenaba como cadenas dínamicamente: por ejemplo, una línea en pantalla de 12 caracteres se almacenan como sólo los 12 caracteres seguidos por el código para "NEWLINE".

También tuvo una interfaz de serie RS-232 por cerca de 140 dólares, y una interfaz paralela Centronics por cerca de 105 dólares, que permitiría al ZX81 comunicarse con una impresora estándar, como también un teclado externo de tamaño normal por cerca de 85 dólares.

DK'tronics vendió una carcasa y un teclado que, con considerable habilidad, se podía usar para sustituir el teclado de membrana y para contener el computador..

En ambos el ZX80 y el ZX81, la salida vídeo era generada por el chip Z80. En el ZX80, cuando un programa formaba, la imagen del televisor se movía desde el principio para comenzar una nueva imagen. Como un loop FOR-NEXT de 1 a 1000 tardaba 19 segundos, fue común hacer funcionar la máquina en modo rápido todo el tiempo, hasta al editar un programa. Esto hacía destellar la imagen del televisor siempre y cuando una tecla era presionada.

Operación técnica del vídeo en el ZX81

editarLos medios técnicos usados para implementar la generación del vídeo para la pantalla del televisor, aunque brillantes, no fueron completamente estándares. El sistema funcionaba como sigue:

El ZX81 contiene, según el tipo de RAM, cuatro chips: una RAM, una ROM, un CPU y un ASIC, llamado en ese entonces ULA – (Uncommitted Logic Array). Unas resistencias fueron colocadas en serie con las líneas de datos. El CPU y la memoria ROM estaban a un lado de las resistencias de datos y la memoria RAM en el otro. Las direcciones 0-8191 estaban asignadas a la ROM, en los últimos 512 bytes, estuvieron contenidas las imágenes de mapa de bits del juego de caracteres, y las direcciones 16384-32767 estaban asignadas para la memoria RAM.

El vídeo de la pantalla era manejado por interrupciones, de tal manera que el proceso normal del computador pudiera seguir durante o cerca del intervalo de blanqueo vertical. Las interrupciones pasaban el control a las rutinas que generaban el vídeo durante el resto del tiempo disponible; entonces, la propia CPU era utilizada como un contador para controlar la salida de los datos de vídeo, desde la memoria hacia la pantalla de TV.

El procesador trataría de saltar, en la memoria RAM, a la dirección 32768 + el principio de los datos de vídeo. Entonces, se activaban simultáneamente, la línea A15 del bus de direcciones, y una raramente usada línea de control del procesador Z80, que indicaba "ciclo de instrucción de memoria 1". El ULA detectaría esto como un intento de ejecutar una instrucción desde la memoria RAM que representa el vídeo y capturaría los datos recuperados del bus de datos. Entonces, comprobaría el bit 6 del dato - de ser cero, el ULA colocaría en el bus de datos, para el consumo del Z80, una instrucción NOP (No OPeración) que para este procesador anda representado con un byte con todos los bits en cero. El CPU continuaría "ejecutando" la RAM del vídeo de esta manera, como si fuera código de máquina del Z80, hasta que se encontrara un byte con bit 6 = 1. Este byte no sería convertido a cero por el ULA y se ejecutaría normalmente por el CPU.

El ZX81 utilizó su propio juego de caracteres no estándar. Los códigos 0-63 eran caracteres imprimibles y los códigos 128-191 era los mismos caracteres en vídeo inverso. El único byte válido con bit 6 = 1 que se podía escribir en la memoria de vídeo era el 118, que representaba la instrucción HALT en el Z80 y hacía que el procesador se detuviera. Este byte fue utilizado como el carácter de nueva línea.

Exceptuando la instrucción HALT, si se hubiera colocado cualquier otro byte con bit 6 = 1 en la RAM de vídeo del ZX81, la máquina se hubiera estrellado casi inmediatamente, ya que se estarían ejecutando instrucciones al azar, sin sentido y sin control.

Una interrupción no enmascarable sería usada entonces para sacar al procesador del estado de HALT, una vez que fuera el momento de mostrar la siguiente línea de la trama.

La conversión de los caracteres en los píxeles para la pantalla estaba basada también en el empleo de capacidades específicas del procesador Z80. El Z80 tiene un registro R, que originalmente fue pensado como un contador para hacer el refrescamiento de la memoria RAM dinámica. Durante un ciclo en que los datos no eran recuperados, la señal de control RFSH estaría activa y el contenido del contador R salía a la porción más baja del bus de direcciones. El registro de vector de interrupción I, se usaba de una manera diferente de la esperada. Una característica no documentada del Z80 ponía el contenido del registro I, en la porción superior del bus de direcciones durante este ciclo de refrescamiento.

El ZX81 tenía el mapa de bits del juego de caracteres al final de los 8 kB de la ROM del BASIC. La ROM estaba conectada al lado opuesto de las resistencias en serie del bus de dirección de tal manera que ciertos bits de dirección podían sobrescribirse bajo control de la ULA. El registro I podía ser cargado para apuntar a la base de la tabla del mapa de bits del juego de caracteres en la ROM y el registro contador (de refrescamiento) R también se podía usar para contar cual línea en el mapa de bits de 8x8 de un carácter debía ser exhibida.

El intérprete del BASIC en sí mismo era completamente propietario, a diferencia de la mayoría de los microcomputadores del momento, excepto el Apple II, que usaron una serie de variantes similares pero incompatibles del BASIC de Microsoft. Quiso decir que no se necesitaba cumplir con el código ASCII o cualquier otro estándar existente.

Incluso la instrucción más simple del Z80 toma cuatro ciclos para ejecutarse. Durante el primer ciclo, el procesador procuraría "ejecutar" el texto del vídeo como dato. El ULA capturaría y guardaría el dato y forzaría, en el bus de datos, la instrucción NOP, (No OPeración) que era representada con un byte con todos los bits a cero. Durante el tercer ciclo, el procesador intentaría un ciclo de refrescamiento para la memoria RAM dinámica. El ULA utilizaría el ciclo de refrescamiento para sustituir el contenido de las líneas de dirección A3-8 del bus de dirección con los bits 0-5 del carácter almacenado. Los bits altos estarían viniendo del registro del vector de interrupciones (que estaba apuntando al juego de caracteres en la ROM), los tres bits más bajos indicarían cual fila del carácter individual era actualmente explorada. El bit 7 del byte original del carácter, sería usado internamente por el ULA para controlar el vídeo inverso del carácter. De esta manera, un byte de píxels para la pantalla sería forzado en el bus donde entonces podía ser alimentado a un registro de desplazamiento manejado por el mismo cristal usado para generar el reloj del CPU y de allí ser enviado al aparato de televisión.

La sincronización del vídeo sería generada usando el mismo bit individual de I/O (E/S) que se usaba para generar la salida para la interfaz de la grabadora de casetes de 250 bit/s.

Por desgracia, si la pantalla estaba activada, el uso de la CPU para generar el vídeo retardaba el procesamiento para las demás cosas en un 75%.

El I/O en sí mismo también utilizó algunas características indocumentadas del Z80. Nominalmente, una dirección de puerto de I/O en el Z80 es de ocho bits. Si un registro de 8 bits es usado como la dirección (por ejemplo la instrucción IN A, [L]) lo que salía realmente por el bus de dirección de 16 bits del Z80 no era el registro L sino el par de registros HL de 16 bits, con L como los ocho bits más bajos. El ZX81 explotó esto usando los ocho bits superiores del bus de dirección para manejar las líneas de exploración para la matriz 8x5 del teclado. Los bits devueltos se podían entonces leer por un solo puerto de la entrada.

Los ocho bits más bajos de la dirección de I/O eran usados como selectores de chips para dispositivos individuales de I/O dentro de la ULA. En la configuración estándar, a menos que la impresora térmica externa opcional estuviera enchufada en el conector de borde de tarjeta del bus de 40 pines, las únicas entradas/salidas presentes eran: un bit para la entrada del casete, un bit para la salida del casete y también usado para la sincronización de vídeo, una palabra de cinco bits para la entrada del teclado y los registros de control requeridos para permitir activar la ULA en sí misma para la generación vídeo. Esto significó que no todos los ocho bits fueron usados, permitiendo algún espacio limitado para extensión externa.

La memoria RAM estuvo limitada originalmente a 2 kilobytes internos; las versiones Timex instalaron la memoria RAM en su totalidad, 2 Kx8 en un chip, mientras que el ZX81s tuvo una memoria RAM estática 1 Kx8 o dos de 1 Kx4, o una de 16 kilobytes externa. En la memoria RAM externa, una línea RAMCS en el pin 40 del bus de expansión era conectada a un nivel constante en el RAMpack para inhabilitar la RAM interna, esto debido al uso de M1 + A15 para indicar la recuperación de los bytes de los caracteres de vídeo.

El RAM pack externo usaba ocho chips 4116 DRAM, una primitiva memoria RAM dinámica de 16 kilobytes × 1 bit en un DIP de 16 pines, con un pin de dato, 7 pines de direcciones multiplexadas, !RAS, !CAS, !WE y energía. Estos viejos chips requerían +12 V, +5 V y -5 V mientras que la fuente de alimentación interna del ZX81 era simplemente un chip 7805, un regulador lineal 5V unido a un pequeño disipador de calor de metal que llegaba a estar algo caliente debido a que el ZX81 fue alimentado por un adaptador de 9 V con un enchufe de 1/8 de pulgada. El RAM pack contenía un oscilador y algunos inductores para convertir los +5 V en los otros voltajes requeridos así como también circuitos para multiplexar las líneas de dirección. Todo esto añadía significativa complejidad interna al RAM pack.

Desafortunadamente, el borde del conector del bus de 40 pines en sí mismo no tenía un recubrimiento de oro-plata: los contactos fueron cubiertos simplemente con soldadura. El ZX81 actualizado fue muy propenso a malas conexiones y a oxidación que lo hicieron mecánicamente muy frágil y propenso a estrellarse. Esto llegó a ser molesto, ya que tomaba ocho minutos recargar completamente los 16 kilobytes de RAM desde una cinta de casete que a menudo no era fiable. Soluciones improvisadas hechas en casa para este problema iban desde físicamente fijar la computadora y el RAM pack a un substrato sólido, hasta poner todo el conjunto en una carcasa más grande con un apropiado teclado sobrante en lugar del original.

Otra mejora menos común hecha por algunos usuarios finales era conectar la RAM estática como "pseudo-ROM" en lugar de la ROM espejo en las direcciones 8192-16383. Al igual que la ROM, esta RAM necesitaría ser conectada en el mismo lado de las resistencias del bus de datos, de modo que pudiera ser utilizada para almacenar un juego de hasta 64 caracteres definido por el usuario. Una variante en este tema añadía un latch de un bit para guardar el más alto bit del carácter original, cuando M1 y A15 estuvieran activas simultáneamente, y usarlo para manejar uno de los bits de dirección, permitiendo que los mapas de bits de todos los 128 caracteres pudieran ser redefinidos.

Mientras que la RAM principal estaba en el lado incorrecto de los resistores del bus de los datos y de dirección para que esto trabajase, el RAM estático adicional era requerido para este enfoque. Cargar el registro I para apuntar al RAM principal no produciría el resultado deseado, en lugar de eso, mostraba basura como píxeles.

Clones

editarEn los Estados Unidos, el ZX81 fue vendido directamente desde Inglaterra y también en asociación con Timex, que lanzó el clon TS-1000.

En la Argentina, el fabricante de motores Czerweny le encargó a la división portuguesa de Timex-Sinclair la producción bajo su propia marca de los modelos TS-1000 (CZ-1000) y TS-1500 (CZ-1500). Seguramente, por motivos ajenos a Czerweny (quizás por el cierre de Timex) había de diseñar y producir sus propios clones a los que denominó CZ-1000 Plus y CZ-1500 Plus, respectivamente. El nuevo diseño incluyó de fábrica el botón de reinicio, una ranura para joysticks de norma Sinclair y salida directa a monitor. Estos modelos tuvieron cierta popularidad en la Argentina, aunque no demasiada como uno de los clones del ZX Spectrum (el CZ-2000).

En Brasil, hubo varias empresas que clonaron el ZX81. Los más importantes fueron Microdigital y Prológica. Microdigital produjo varios clones del ZX80 (el TK 80 y el TK 82/82C), un clon del ZX81 (el TK 83), un clon del TS-1500 (el TK 85), y dos clones del ZX Spectrum (el TK 90X y el TK 95). Prológica produjo el NE-Z80 (un clon del ZX80), el NEZ-8000, el CP-200 y el CP-200S (la última de ellas como una versión económica).

Véase también

editarEnlaces externos

editar- Planet Sinclair:ZX81

- EightyOne ZX81 Emulator for Windows (GPL)

- z81 – Sinclair ZX81 and ZX80 emulator (GPL)

- ZEsarUX - ZX Second-Emulator And Released for UniX (GPL)

- ZX81Kit - ZX81 Kits still for sale!

- ZX81 & G007 Hi-Res Graphics

- The ZX81 manual

- ZX81 The Archive

- Sinclair ZX81 books, software, hardware and peripherals