Saturn (microprocesador)

La familia Saturn de microprocesadores de 4 bits (bus de datos) fue desarrollada por Hewlett-Packard en la década de 1980, primero para la computadora de mano HP-71B y luego para varias calculadoras HP (comenzando con la HP-18C). Reemplazó a la familia de procesadores Nut utilizada en calculadoras anteriores. El circuito integrado Saturn original se usó por primera vez en la computadora portátil HP-71B programable en BASIC, presentada en 1984. Los modelos posteriores de la familia impulsaron la popular de calculadoras de la serie HP-48. Las HP48SX y HP48S fueron los últimos modelos en utilizar procesadores Saturn originales fabricados por HP. Los modelos de calculadoras posteriores utilizaron procesadores Saturn fabricados por NEC. La serie HP-49 también usó inicialmente la CPU Saturn, hasta que la fábrica NEC[nb 1] ya no pudo fabricar el procesador por razones técnicas en 2003. Por lo tanto, comenzando con el modelo HP-49G+ en 2003, las calculadoras cambiaron a un procesador Samsung S3C2410 con un núcleo ARM920T (parte de la arquitectura ARMv4T) que ejecutaba el software en un emulador del hardware de Saturn. En 2000, la HP-39G y la HP-40G fueron las últimas calculadoras introducidas basadas en el hardware Saturn fabricado por NEC. Las últimas calculadoras basadas en el emulador Saturn fueron la HP-39GS, HP-40GS y HP-50G en 2006, así como la revisión de 2007 de la HP-48GII. La HP-50G, la última calculadora que utilizó este emulador, se suspendió en 2015 cuando Samsung dejó de producir el procesador ARM en el que se basaba.[1][2][3]

| Saturn | |||||

|---|---|---|---|---|---|

| |||||

| Información | |||||

| Tipo | CISC; combinación de una arquitectura de carga-almacenamiento con algunas excepciones que pertenecen a la familia arquitectura de registro-memoria | ||||

| Desarrollador | Hewlett-Packard | ||||

| Fecha de lanzamiento | 1984 | ||||

| Datos técnicos | |||||

| Conjunto de instrucciones | Híbrido: GPR de 64 bits, bus de direcciones de 20 bits, bus de datos de 4 bits, tamaño de palabra mínimo de 4 bits | ||||

| Cronología | |||||

| |||||

Arquitectura

editarEl hardware de Saturn es un diseño basado en nibble en serie,[4] a diferencia de su predecesor Nut, que era de bits en serie.[5] Internamente, la CPU Saturn tiene cuatro buses de datos de 4 bits que permiten un rendimiento de casi 1 ciclo por nibble con uno o dos buses que actúan como origen y uno o dos que actúan como destino. La palabra direccionable más pequeña es un nibble de 4 bits que puede contener un dígito decimal codificado en binario (BCD). Cualquier unidad de datos en los registros mayor que un nibble, en los que el final de dicha unidad de datos cae en un límite de un nibble y el comienzo de dicha unidad de datos comienza en un nibble cero (y también en algunos casos en los que la posición inicial de dicha unidad de datos cae en un límite de nibble con ciertos campos de registro, por ejemplo, «M» o «X»), y que puede tener hasta 64 bits, se puede operar como un todo, pero la CPU de Saturn realiza la operación internamente en una base nibble a nibble.[4]

La arquitectura Saturn tiene un ancho de palabra de datos de 64 bits y un ancho de direcciones de 20 bits, y la memoria es direccionada de a 4 bits (nibble). Las instrucciones ALU Saturn admiten un ancho de datos variable, operando en uno a 16 nibbles de una palabra. Los registros principales (GPR), junto con los registros temporales, tienen un ancho completo de 64 bits, pero los registros de dirección tienen solo 20 bits de ancho. Los chips de CPU Saturn originales proporcionaban un bus de datos externo de cuatro bits, pero los SoC basados en Saturn posteriores incluyeron la conversión del bus del chip a un bus de datos externo de 8 bits y un bus de direcciones externo de 19 bits.

La arquitectura Saturn tiene cuatro GPR (Registros de propósito general) de 64 bits, llamados A, B, C y D. Además, también hay cinco registros termporales de 64 bits llamados R0, R1, R2, R3 y R4. Estos solo pueden almacenar datos. Si se requiere una operación ALU para datos en un registro temporal, entonces el registro en cuestión debe transferirse primero a un GPR. Otros registros incluyen un registro de «puntero» de 1 nibble llamado P, generalmente utilizado para seleccionar un nibble en un GPR o un rango de nibbles (o para alinear datos inmediatos en un nibble específico en un GPR, con envoltura). Para el acceso a la memoria, hay dos registros de puntero de datos de 20 bits llamados D0 y D1. La arquitectura Saturn también tiene un registro de PC o contador de programa que puede interoperar con los GPR. También hay una pila de retorno de hardware LIFO circular de 8 niveles y 20 bits denominada RSTK que se utiliza cuando se emite una instrucción de llamada a subrutina. Además, la CPU Saturn está equipada con un registro de estado de software de 16 bits llamado ST y un registro de estado de hardware de 1 nibble llamado HS, que en particular contiene el indicador SB o «sticky bit» que indica si un 1 binario se desplazó a la derecha de un GPR. Además, la arquitectura Saturn tiene un registro de SALIDA de 12 bits y un registro de ENTRADA de 16 bits, que en los SoC de Yorke y Clarke se utilizan para capturar la entrada del teclado y también para controlar el bíper. También hay un registro de bandera de acarreo de 1 bit.

Además de lo anterior, la CPU Saturn tiene un sistema de interrupción simple y no priorizado. Cuando ocurre una interrupción, la CPU termina de ejecutar la instrucción actual, guarda el contador del programa en la pila de retorno de hardware (RSTK) y salta a la dirección hexadecimal 0x0000Fh, donde el valor anterior está en nibbles.[4] La CPU también interactúa directamente con la lógica de escaneo del teclado.

El siguiente diagrama muestra los registros (cada cuadrado blanco tiene 4 bits/un nibble, excepto la bandera de acarreo, que tiene 1 bit):

Campos y formato de registros GPR de 64 bits del Saturn:

| Bits | 63-60 | 59-56 | 55-52 | 51-48 | 47-44 | 43-40 | 39-36 | 35-32 | 31-28 | 27-24 | 23-20 | 19-16 | 15-12 | 11-8 | 7-4 | 3-0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Nibble | F | E | D | C | B | A | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Campos | XS | B | |||||||||||||||

| A | |||||||||||||||||

| S | M | X | |||||||||||||||

| W | |||||||||||||||||

| P=0 | P | ||||||||||||||||

| P=7 | WP | ||||||||||||||||

Se puede acceder a los datos en los registros de propósito general a través de campos que caen en los límites de nibble, mientras que los registros temporales solo permiten operaciones de carga y almacenamiento. Los campos, como se muestra en el diagrama anterior, son W (GPR completo de 64 bits), A (primeros 5 nibbles de un GPR), S (nibble más significativo de un GPR), XS (nibble 2 de un GPR), M (nibbles 3-14 de un GPR), X (primeros 3 nibbles de un GPR) y B (primer byte de un GPR). Además, existe el campo P que selecciona un nibble de un GPR basado en el valor de 4 bits del registro P. Además, existe el campo WP que selecciona nibbles 0 a través del nibble seleccionado en el registro P. Los 64 bits (16 nibbles) pueden contener números de coma flotante codificados con formato BCD compuestos por un signo nibble (que es "9" si el número es negativo), 12 dígitos de mantisa y un exponente de 3 dígitos de complemento a 10 almacenados en formato BCD (±499).[6] La representación interna de los valores de coma flotante BCD es una mantisa de 15 dígitos con un nibble de signo en un registro combinado con un exponente de 20 bits, en formato de complemento a 10, en otro registro. El uso de BCD en lugar de la representación binaria directa es ventajoso para las calculadoras, ya que evita problemas de redondeo que ocurren en la conversión binaria/decimal.

Las direcciones de la CPU Saturn también se basan en nibble. Los tres registros de punteros (incluidos el contador de programa) y de direcciones tienen 20 bits de ancho. Debido a esto, la arquitectura Saturn puede abordar 1 M nibbles o, de manera equivalente, 512 K bytes. Más allá de ese tamaño (por ejemplo, en el 48GX), se utiliza la conmutación de bancos de memoria.

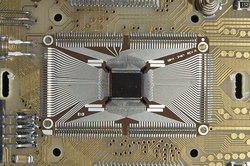

En las series HP 48S/SX y 48G/GX, y también en calculadoras como la HP-28S, HP-42S, HP-32SII y HP-20S, el núcleo de la CPU Saturn está integrado como parte de un circuito integrado más complejo, un paquete SoC, excepto para la computadora de mano original HP-71B y la HP-28C que usaba un chip separado para el procesador Saturn. Estos paquetes tienen nombres en clave inspirados en los miembros de la expedición de Lewis y Clark. El nombre en clave del IC es Clarke en el S/SX, por William Clark, y Yorke en el G/GX, por el criado de Clark. Otros circuitos integrados basados en Saturn, como los utilizados en HP-28S, HP-42S, HP-32SII y HP-20S, tenían otros nombres en clave. Específicamente, el SoC HP-42S y HP-28S recibió el nombre en código de Lewis, en honor a Meriwether Lewis. Otras calculadoras HP, como la HP-32SII y la HP-20S, tenían SoC con el nombre en código Sacajawea, en honor a Sacagawea, y Bert, respectivamente, aunque es posible que se desconozca el origen del nombre en código Bert.

Código de ejemplo

editarLa siguiente es una implementación de enteros de un algoritmo de raíz cuadrada decimal BCD en la sintaxis de ensamblador de Saturn Jazz/HP Tools:

** En lo siguiente, se supone que A.W contiene el argumento (< 1E14).

** El resultado (IP(SQRT(A.W))) está en C.W:

SETDEC

ASL W

C=A W

A=A+A W

A=A+A W

A=A+C W

ASR W

C=0 W

P= 13

LC(1) 5

- CSR WP

C=C-1 P

-- C=C+1 P

A=A-C W

GONC --

A=A+C W

CSR W

P=P-1

P=P-1

GONC -

SETHEX

A=C W

Chipsets y aplicaciones

editarEl CPU Saturn original dio su nombre a toda la arquitectura. Más tarde, los chips tenían sus propios nombres en clave:

| Nivel ISA | Nombre en código | Usado en modelos de calculadora | Propiedades |

|---|---|---|---|

| 0[7][8] | Saturn (1LF2) | HP-44A, HP-71B (1984) | |

| 1[7][8] | Saturn (1LK7) | HP-18C (1986), HP-28C (1987), HP-71B | 640 kHz, más instrucciones |

| 2[7][8] | Bert[9] (1LU7)[9] | HP-10B (1988), HP-20S (1988), HP-21S | 640 kHz, 10 KB ROM, 256 bytes RAM, driver LCD |

| 2[7][8] | Sacajawea[9] (1LR3) | HP-14B, HP-22S, HP-32S (1988), HP-32S+, HP-32SII (1991) | 640 kHz, 16 KB ROM, 512 bytes RAM, driver LCD |

| 2[7][8] | Lewis[9] (1LR2) | HP-17B (1988), HP-17BII (1990), HP-19B (1988), HP-19BII (1990), HP-27S (1988), HP-28S (1988), HP-42S (1988) | 1 MHz, 64 KB ROM, driver LCD, controlador de memoria, control IR, CMOS 3V |

| 2[7][8] | Clarke[9] (1LT8)[9] | HP-48SX (1990), HP-48S (1991) | 2 MHz, controlador LCD, controlador de memoria, UART y control IR, más instrucciones |

| 2[7][8] | Yorke[9] 00048-80063[10] | HP-38G (1995), HP-38G+ (1998), HP-39G (2000), HP-40G (2000), HP-48GX (1993), HP-48G (1993),[nb 1] HP-48G+ (1998), HP-49G (1999) | 3,68-4 MHz, controlador LCD, controlador de memoria, UART y control IR, fabricado por NEC, más instrucciones, a veces conocido como plataforma Saturn 5 |

| ? | New-Yorke | HP-48GX prototipo | 8 MHz, controlador LCD, controlador de memoria, UART y control IR. Esto solo se hizo como un prototipo interno de HP y nunca se lanzó en la naturaleza.[11]< |

| 2[7][8][nb 2] | serie Apple (Big Apple,[9] Mid Apple,[9] Little Apple) | HP-39G+ (2003), HP-39GS (2006), HP-40GS (2006), HP-49G+ (2003), HP-48GII (2003/2007), HP-50G (2006) | Virtual versión de la CPU Yorke emulatda por miembros de procesadores de la familia Samsung S3C2410 a 48/75 MHz con núcleo ARM920T (de la arquitectura ARMv4T), también conocido como Saturn+, con instrucciones virtuales adicional |

Los nombres en clave de la CPU están inspirados en los miembros de la expedición de Lewis y Clark de 1804-1806, la primera expedición por tierra de los Estados Unidos a la costa del Pacífico y regreso. Los nombres en código de la CPU virtual/emulada se inspiraron en el prototipo de SoC de 8 MHz basado en Saturn "New-Yorke" que nunca llegó a la producción.[12] ), «Big Apple» se derivó del nombre en clave «New-Yorke» del prototipo SoC basado en Saturn de 8 MHz, y que para el autor original parecía insinuar una referencia a «Nueva York», la ciudad, de ahí los nombres «Big Apple», «Mid Apple» y «Little Apple».[12]

Referencias

editar- ↑ Kuperus, Klaas (4 de marzo de 2015). «HP 50g: End of an era». forum.hp-prime.de. Moravia. Archivado desde el original el 2 de abril de 2015.

- ↑ Kuperus, Klaas (6 de marzo de 2015). «HP 50g not so good news?». HP Museum. Moravia. Archivado desde el original el 8 de julio de 2018. Consultado el 1 de enero de 2016.

- ↑ Wessman, Timothy James (26 de diciembre de 2015). «Windows 10 won't allow HP 50g USB drivers to be installed». HP Museum. Archivado desde el original el 8 de julio de 2018. Consultado el 1 de enero de 2016.

- ↑ a b c HP-71B Hardware Internal Design Specification Vol 1. Hewlett Packard Corporation. September 1984. p. 3-1.

- ↑ HP-41C CPU, Display Driver, HP-IL, Data Storage, Timer IC, and Interface IC Specifications. Hewlett Packard Corporation. July 1981. p. 5.

- ↑ Fernandes, Gilbert (16 de julio de 2005). Chapter 56.1 Real number. En Rechlin, Eric, ed. «Introduction to Saturn Assembly Language». hpcalc.org (3rd edición). p. 104. ID 1693. Archivado desde el original el 13 de noviembre de 2018. Consultado el 29 de abril de 2019. «If the exponent is negative, the exponent is encoded as "1000 - ABS(exponent)"». [1]

- ↑ a b c d e f g h Donnini, Giuseppe (26 de junio de 2020). «"New-Yorke" ?». www.hpmuseum.org. Consultado el 6 de julio de 2020.

- ↑ a b c d e f g h «The Saturn assembler manual». www.hpcalc.org. Hewlett Packard. 20 de agosto de 1993. Consultado el 6 de julio de 2020.

- ↑ a b c d e f g h i Finseth, Craig A. (23 de diciembre de 2016). «names». Archivado desde el original el 21 de diciembre de 2017. Consultado el 21 de diciembre de 2017.

- ↑ (1994-05-03). "Name that chip!". comp.sys.hp48. (Google Groups).

- ↑ de Brébisson, Cyrille (17 de junio de 2020). «RE: "New-Yorke" ?». www.hpmuseum.org. Consultado el 18 de junio de 2020.

- ↑ a b de Brébisson, Cyrille (16 de junio de 2020). «RE: "New-Yorke" ?». www.hpmuseum.org. Consultado el 18 de junio de 2020.

Notas

editarEnlaces externos

editar- Una guía para el procesador Saturn.

- Información resumida en el museo de calculadoras HP.

- Fernandes. Eric PDF, ed. Introducción al Lenguaje Ensamblador Saturn.

- Véase también Paul Courbis's libros que contienen información acerca de la programación del Saturn.